# **AW-HM482**

# **IEEE 802.11ah Wireless LAN Module**

# **Layout Guide**

Rev. 0.1

(For Standard)

# **Revision History**

Document NO:

| Version | Revision<br>Date | DCN NO. | Description     | Initials      | Approved   |

|---------|------------------|---------|-----------------|---------------|------------|

| 0.1     | 2021/2/22        |         | Initial Version | Daniel<br>Lee | NC<br>Chen |

|         |                  |         |                 |               |            |

# **Table of Contents**

| Revision History                                   |   |

|----------------------------------------------------|---|

| Table of Contents                                  | 3 |

| 1 Overview                                         |   |

| 1.1 Device supported                               |   |

| 2 GENERAL RF GUIDELINES                            |   |

| 3 Ground Layout                                    |   |

| 4 Power Layout                                     |   |

| 5 Digital Interface                                |   |

| 6 RF Trace                                         |   |

| 7 Antenna                                          | 7 |

| 8 Antenna Matching                                 |   |

| 9 SHIELDING CASE                                   |   |

| 10 GENERAL LAYOUT GUIDELINES                       |   |

| 11 The other layout guide Information              |   |

| 12 LGA module layout footprint recommend           |   |

| 12.1 LGA Module stencil and Pad opening Suggestion |   |

### 1 Overview

#### 1.1 Device supported

This document provides key guidelines and recommendations to be followed when creating AW-HM482 (18 x 24 mm LGA Module) layout. It is strongly recommended that layouts be reviewed by the AzureWave engineering team before being released for fabrication.

The following is a summary of the major items that are covered in detail in this application note. Each of these areas of the layout should be carefully reviewed against the provided recommendations before the PCB goes to fabrication.

#### 2 GENERAL RF GUIDELINES

Follow these steps for optimal WLAN performance.

- 1. Control WLAN 50 ohm RF traces by doing the following:

- Route traces on the top layer as much as possible and use a continuous reference ground plane underneath them.

- Verify trace distance from ground flooding. At a minimum, there should be a gap equal to the width of one trace between the trace and ground flooding. Also keep RF signal lines away from metal shields. This will ensure that the shield does not detune the signals or allow for spurious signals to be coupled in.

- Keep all trace routing inside the ground plane area by at least the width of a trace.

- Check for RF trace stubs, particularly when bypassing a circuit.

- 2. Keep RF traces properly isolated by doing the following:

- Do not route any digital or analog signal traces between the RF traces and the reference ground.

- Keep the pins and traces associated with RF inputs away from RF outputs. If two RF traces are close each other, then make sure there is enough room between them to provide isolation with ground fill.

- Verify that there are plenty of ground vias in the shield attachment area. Also verify that there are no non-ground vias in the shield attachment area. Avoid traces crossing into the shield area on the shield layer.

- 3. Consider the following RF design practices:

- Verify that the RF path is short, smooth, and neat. Use curved traces for all turns; never use 90-degree turns. Avoid width discontinuities over pads. If trace widths differ significantly from component pad widths, then the width change should be mitered. Verify there are no stubs.

- Do not use thermals on RF traces because of their high loss.

- The RF traces between AW-HM482 RF\_ANT pin and antenna must be made using  $50\Omega$  controlled-impedance transmission line.

## 3 Ground Layout

Please follow general ground layout guidelines. Here are some general rules for customers' reference.

- •The layer 2 of PCB should be a complete ground plane. The rule has to be obeyed strictly in the RF section while RF traces are on the top layer.

- •Each ground pad of components on top layer should have via drilled to PCB layer 2 and via should be as close to pad as possible. A bulk decoupling capacitor needs two or more.

- •Don't place ground plane and route signal trace below printed antenna or chip antenna to avoid destroying its electromagnetic field, and there is no organic coating on printed antenna. Check antenna chip vendor for the layout guideline and clearance.

- •Move GND vias close to the pads.

## **4 Power Layout**

Please follow general power layout guidelines. Here are some general rules for customers' reference.

- •A 10uF capacitor is used to decouple high frequency noise at digital and RF power terminals. This capacitor should be placed as close to power terminals as possible.

- •In order to reduce PCB's parasitic effects, placing more via on ground plane is better.

### **5 Digital Interface**

Please follow power and ground layout guidelines. Here are some general rules for customers' reference.

- •The digital interface to the module must be routed using good engineering practices to minimize coupling to power planes and other digital signals.

- •The digital interface must be isolated from RF trace.

#### 6 RF Trace

The RF trace is the critical to route. Here are some general rules for customers' reference.

- •The RF trace impedance should be  $50\Omega$  between ANT port and antenna matching network.

- •The length of the RF trace should be minimized.

- •To reduce the signal loss, RF trace should laid on the top of PCB and avoid any via on it.

- •The CPW (coplanar waveguide) design and the microstrip line are both recommended; the customers can choose either one depending on the PCB stack of their products.

- •The RF trace must be isolated with aground beneath it. Other signal traces should be isolated from the RF trace either by ground plane or ground vias to avoid coupling.

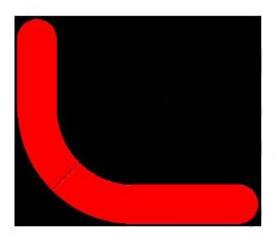

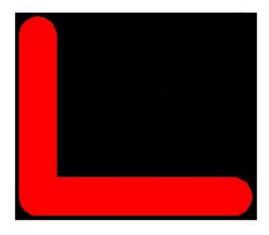

- •To minimize the parasitic capacitance related to the corner of the RF trace, the right angle corner is not recommended.

If the customers have any problem in calculation of trace impedance, please contact AzureWave.

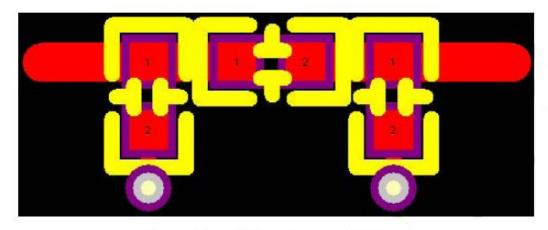

**Correct RF trace**

Via on RF trace

**Incorrect RF trace**

#### 7 Antenna

All the high-speed traces should be moved far away from the antenna. For the best radiation performance, check antenna chip vendor for the layout guideline and clearance.

# 8 Antenna Matching

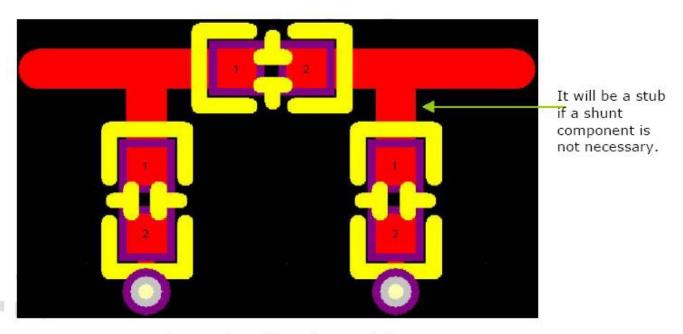

PCB designer should reserve an antenna matching network for post tuning to ensure the antenna performance in different environments. Matching components should be close to each other. Stubs should also be avoided to reduce parasitic while no shunt component is necessary after tuning.

Correct layout for antenna matching

Incorrent layut for antenna matching

#### 9 SHIELDING CASE

Magnetic shielding, ferrite drum shielding, or magnetic-resin coated shielding is highly recommended to prevent EMI issues.

#### 10 GENERAL LAYOUT GUIDELINES

Follow these guidelines to obtain good signal integrity and avoid EMI:

- 1. Place components and route signals using the following design practices:

- Keep analog and digital circuits in separate areas.

- Orient adjacent-layer traces so that they are perpendicular to one another to reduce crosstalk.

- Keep critical traces on internal layers, where possible, to reduce emissions and improve immunity to external noise. However, RF traces should be routed on outside layers to avoid the use of vias on these traces.

- Keep all trace lengths to a practical minimum. Keep traces, especially RF traces, straight wherever possible. Where turns are necessary, use curved traces or two 45-degree turns. Never use 90-degree turns.

- 2. Consider the following with respect to ground and power supply planes:

- Route all supply voltages to minimize capacitive coupling to other supplies. Capacitive coupling can occur if supply traces on adjacent layers overlap. Supplies should be separated from each other in the stack-up by a ground plane, or they should be coplanar (routed on different areas of the same layer).

- Provide an effective ground plane. Keep ground impedance as low as possible. Provide as much ground plane as possible and avoid discontinuities. Use as many ground vias as possible to connect all ground layers together.

- Maximize the width of power traces. Verify that they are wide enough to support target currents, and that they can do so with margin. Verify that there are enough vias if the traces need to change layers.

- 3. Consider these power supply decoupling practices:

- Place decoupling capacitors near target power pins. If possible, keep them on the same side as the IC they decouple to avoid vias that add inductance.

- Use appropriate capacitance values for the target circuit.

## 11 The other layout guide Information

- High speed interface (i.e. UART/SPI) shall have equal electrical length. Keep them away from noise sensitive blocks.

- Good power integrity of VDDIO will improve the signal integrity of digital interfaces.

- Good return path and well shielded signal can reduce crosstalk, EMI emission and improve signal integrity.

- RF IO is around 50 ohms, reserve Pi or T matching network to have better signal transition from port to port.

- Smooth RF trace help to reduce insertion loss. Do not use 90 degrees turn (use two 45 degrees turns or one miter bend instead).

- Discuss with AzureWave Engineer after you finish schematic and layout job.

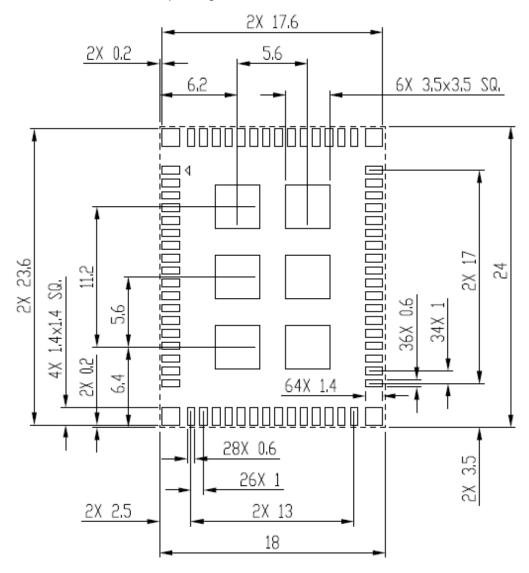

# 12 LGA module layout footprint recommend

## 12.1 LGA Module stencil and Pad opening Suggestion

Stencil thickness: 0.1~0.12mm

Function Pad opening size suggestion: Max. 1:1

PS: This opening suggestion just for customer reference, please discuss with AzureWave's Engineer before you start SMT.

18x24mm Solder Printer Opening Reference:

RECOMMENDED PCB LAYOUT (TOP VIEW)